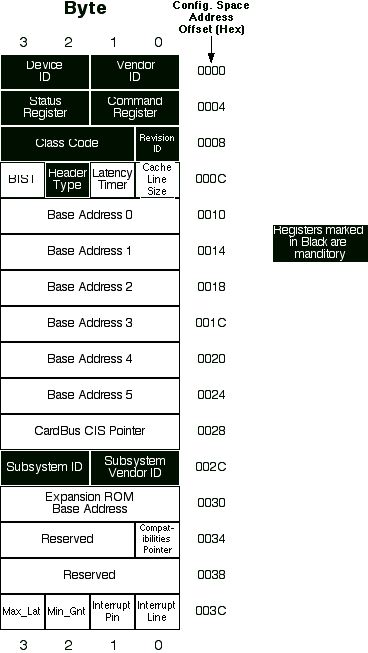

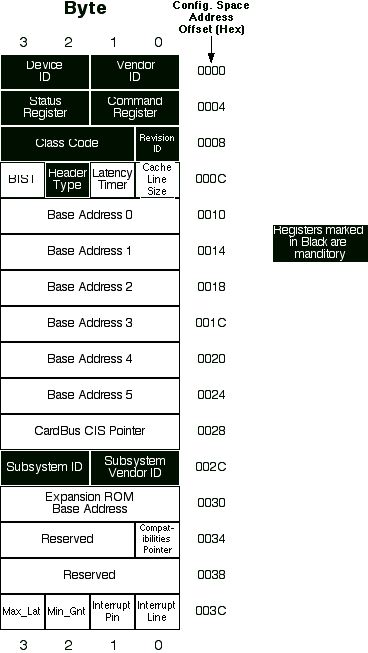

The PCI configuration header

#include <pci.h>

Data Fields | |

| uint16_t | vendor_id |

| The vendor ID of this device. | |

| uint16_t | device_id |

| The device ID of this device. | |

| uint16_t | command |

| By writing to this field the system controls the device. | |

| uint16_t | status |

| This field gives the status of the device with the meaning of the bits of this field set by the standard. | |

| uint8_t | revision_id |

| The revision ID of this device. | |

| uint8_t | interface |

| The interface code of this device. | |

| uint8_t | sub_class |

| The sub-class ID of this device. | |

| uint8_t | base_class |

| The base-class code of this device. | |

| uint8_t | cache_line_size |

| The cache line size. | |

| uint8_t | latency_timer |

| The latency timer. | |

| uint8_t | header_type |

| The header type. | |

| uint8_t | bist |

| Build-in Self Test. If BIST is implemented, can write to a 1 to initiate BIST. | |

| uint8_t | bus |

| The bus number where this device resides. | |

| uint8_t | dev |

| The device number where this device resides. | |

| uint8_t | func |

| The function number where this device resides. | |

| uint8_t | irq |

| The IRQ line (if the device has it! otherwise it is 0). Remeber that a PCI IRQ line can be shared between more than one device. This is a fetature of the PCI devices only. If more than one device shares a IRQ line the software must provide an opportune interrupt handler that recognizes the right device which causes the interrupt and switches the execution between the dedicated routines. | |

| uint32_t | base [6] |

| Base addresses (for both I/O and memory-based devices). Every PCI device has up to 6 base addresses (6 for normal devices, 2 for PCI to PCI bridges and only 1 for cardbuses). | |

| uint32_t | size [6] |

| Size of the I/O space. For memory-based devices it is the size of the memory-mapped buffer; for I/O based devices it is the maximum offset of the ports used. | |

| uint8_t | type [6] |

| Type of the I/O operation (memory based or I/O based). | |

| uint32_t | rom_base |

| The ROM base address. | |

| uint32_t | rom_size |

| The ROM memory space. | |

| uint16_t | subsys_vendor |

| Subsystem vendor ID. | |

| uint16_t | subsys_device |

| Subsystem device ID. | |

| uint8_t | current_state |

| Power management state (from D0 to D3). | |

The PCI configuration header

Definition at line 173 of file pci.h.

|

|

Base addresses (for both I/O and memory-based devices). Every PCI device has up to 6 base addresses (6 for normal devices, 2 for PCI to PCI bridges and only 1 for cardbuses).

|

|

|

The base-class code of this device.

|

|

|

Build-in Self Test. If BIST is implemented, can write to a 1 to initiate BIST.

|

|

|

The bus number where this device resides.

|

|

|

The cache line size.

|

|

|

By writing to this field the system controls the device.

|

|

|

Power management state (from D0 to D3).

|

|

|

The device number where this device resides.

|

|

|

The device ID of this device.

|

|

|

The function number where this device resides.

|

|

|

The header type.

|

|

|

The interface code of this device.

|

|

|

The IRQ line (if the device has it! otherwise it is 0). Remeber that a PCI IRQ line can be shared between more than one device. This is a fetature of the PCI devices only. If more than one device shares a IRQ line the software must provide an opportune interrupt handler that recognizes the right device which causes the interrupt and switches the execution between the dedicated routines.

|

|

|

The latency timer.

|

|

|

The revision ID of this device.

|

|

|

The ROM base address.

|

|

|

The ROM memory space.

|

|

|

Size of the I/O space. For memory-based devices it is the size of the memory-mapped buffer; for I/O based devices it is the maximum offset of the ports used.

|

|

|

This field gives the status of the device with the meaning of the bits of this field set by the standard.

|

|

|

The sub-class ID of this device.

|

|

|

Subsystem device ID.

|

|

|

Subsystem vendor ID.

|

|

|

Type of the I/O operation (memory based or I/O based).

|

|

|

The vendor ID of this device.

|

1.2.18

1.2.18